5 nm精度极紫外干涉技术,助力突破光刻衍射极限

极紫外(EUV)光刻技术是互补金属氧化物半导体(CMOS)量产中一种先进的技术,随着下一代高数值孔径(NA)EUV扫描仪的不断发展,EUV光刻技术正朝着特征尺寸低于10 nm的方向发展。到目前为止,基于透射光栅的EUV干涉光刻技术(EUV-IL)已经成为早期开发EUV光刻胶和相关工艺的图案化工具,在探索和推动光子光刻技术的发展方面发挥了关键作用。然而,由于衍射极限的限制,使用EUV-IL技术实现低于10 nm的特征尺寸仍存在挑战。

瑞士Paul Scherrer研究所(PSI)的研究人员开发了一种新的EUV-IL装置,该装置采用基于反射镜的技术,突破了传统基于光栅方法固有的衍射效率对衍射极限的限制,显著提高了光刻的分辨率,可用于制造更密集的电路模式,有望进一步推进计算机芯片的小型化。相关研究成果以“Extreme ultraviolet lithography reaches 5 nm resolution”为题,发表在Nanoscale上。(原文链接:https://www.photonics.com/Articles/EUV_Lithography_Resolution_Boosted_to_5_nm/p5/a70224)

目前微米级芯片的导电通道一般相隔12 nm,而PSI的研究人员已经成功制造出了5 nm间距的通道。这意味着采用该技术可以设计出比以前更紧凑的电路。Giannopoulos表示,“我们的工作展示了光刻的潜力,这对工业界和学术研究来说都是重要的一步。”

1970年,一个微米级芯片上通常只能容纳大约1000个晶体管。而50多年后的今天,一个仅比指尖大一点的区域就可以容纳大约600亿个元件,这些元件都是用光刻技术制造的。制造流程可以简略概括为:1)在硅晶圆上旋涂上一层光刻胶来构成光敏层;2)将其暴露在与芯片版图相对应的光模式下,可以改变光刻胶的化学性质(溶解性);3)根据使用的正(负)胶,显影去除暴露(未暴露)的区域,在晶圆上留下导电通道,形成所需的布线图案。

长期以来,工业界广泛使用波长为193 nm的深紫外(DUV)光刻技术。自2019年以来,制造商一直在量产中使用波长为13.5 nm的EUV光刻技术;更短波长的极紫外光可以曝光更精细的结构,分辨率低至10 nm或更小。最近在PSI,研究人员使用瑞士光源(SLS)照射并进行探究,最终将入射光波长调整为13.5 nm。

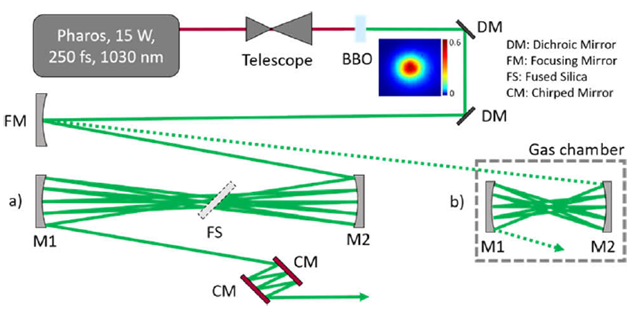

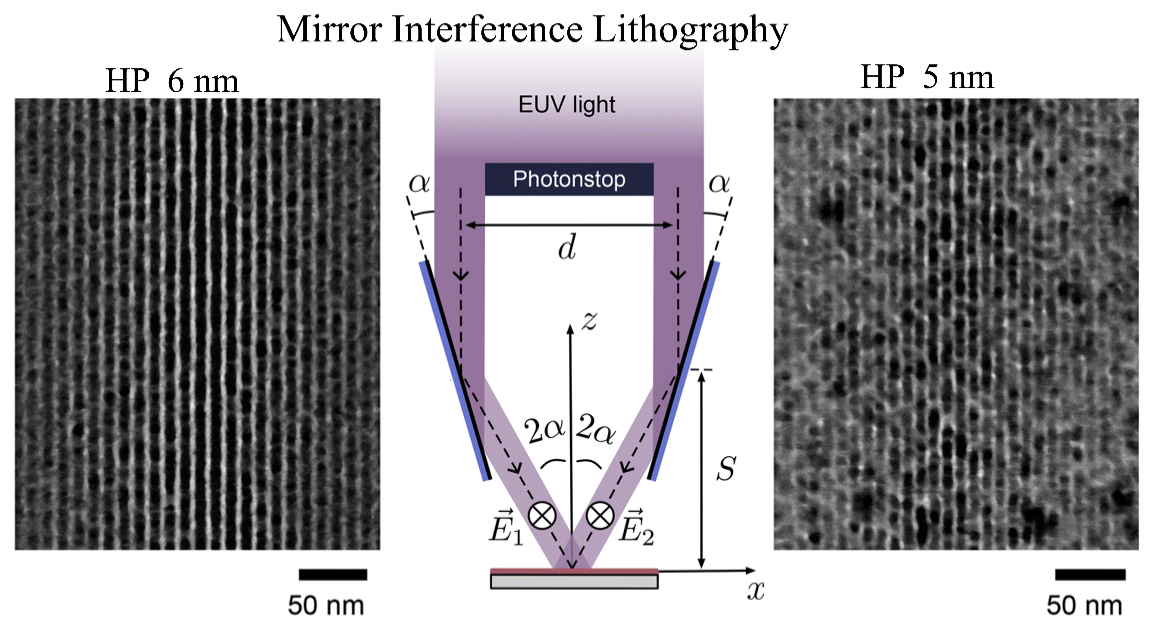

PSI的研究人员通过间接暴露样品扩展了传统的EUV光刻技术。图2是研究人员开发的极紫外光反射镜干涉光刻技术(MIL)的原理示意图,两束相干光通过两个相同的反射镜反射到晶圆上,形成干涉图案,其周期取决于入射角和光的波长。为了评估MIL装置的性能,在高分辨率的HSQ(Hydrogen silsesquioxane,氢倍半硅氧烷)光刻胶上进行图案曝光。通过单次曝光,分别在掠射角(α)17°和21.2°下实现了特征尺寸6 nm和5 nm的干涉图案。

在扫描电子显微镜下观察,发现导电通道具有高对比度和锋利的边缘。Kazazis表示,“我们的实验结果表明EUV光刻技术可以产生极高的分辨率,这意味着目前还没有可预见的根本局限性,这真的很令人兴奋,因为它扩展了我们对可能性的认知边界,并且可以为EUV光刻和光刻胶材料领域的研究开辟新的途径。”

目前,这种方法并不适用于工业界芯片生产,因为与工业标准相比,它的速度较慢,并且只能生产简单和周期性的结构,不能生产具有复杂结构的芯片。但是,它为未来芯片生产所需光刻胶的早期开发提供了一种方法,能实现目前工业界无法达到的分辨率。

该团队表示,他们计划在SLS使用一种新的EUV工具继续他们的研究,该研究将持续到2025年底;新工具与目前正在升级的SLS 2.0相结合,预计将极大地改善性能和功能。

免责声明:本文旨在传递更多科研资讯及分享,所有其他媒、网来源均注明出处,如涉及版权问题,请作者第一时间联系我们,我们将协调进行处理,最终解释权归旭为光电所有。